Когда то меня тоже пугала загадочная аббревиатура – JTAG. Всячески оттягивал момент близкого знакомства с ним, но вот он наступил. В данной статье я хочу рассказать и показать, что не все так просто – многим кажется, что JTAG является неким «шнурком» и все. JTAG следует понимать, как некую технологию, преследующую достижение определенных целей. Итак начнем по порядку.

JTAG Boudaty-Scan Test (BST)

В 1985 сформировалась специальная группа ведущих производителей электроники - JTAG (Joint Test Action Group). Для решения проблем тестирования JTAG выдвинула как промышленный стандарт спецификацию IEEE Std 1149.1-1990 (IEEE Standard Test Access Port and Boundary-Scan Architecture).

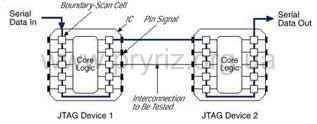

Встраивание архитектуры BST в современные чипы обеспечивает доступ к выводам чипа (точнее, к специальным блокам ввода-вывода) с помощью 4-х проводного последовательного интерфейса JTAG. Эта архитектура позволяет не только контролировать их состояние, но и управлять ими. Таким образом можно обойтись без громоздких пробников с физическим контактом.

В дополнении к этому, эта архитектура может быть дополнена возможностью обмениваться и иной информацией с чипом. Например, получать результат внутреннего теста, как это делается в современных процессорах. В ПЛИС (программируемых логических интегральных схемах) эта архитектура обеспечивает альтернативную (или основную) возможность ввода конфигурационных данных.

Необходимо отметить, что для подобных целей используются также и другие последовательные интерфейсы. Например, 2-х проводный I2C требует меньше аппаратных затрат и, что более важно, времени для доступа к устройствам. Однако, преимуществом архитектуры BST является отсутствие необходимости явного задания адресов устройств, поскольку все JTAG-устройства объединяются в последовательную цепочку и неявно адресуются своим положением в ней.

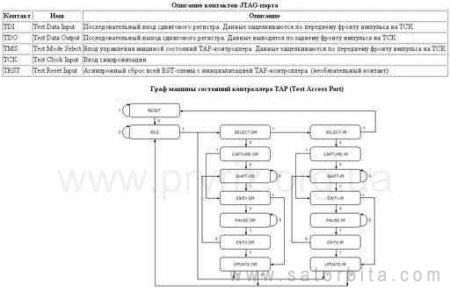

Как видно из графа, TAP-контроллер перейдет в исходное состояние RESET из любого другого не более чем за 5 импульсов TCK при TMS=1. При этом произойдет сброс всей схемы BST, а в регистр инструкций запишется значение по умолчанию (как правило, инструкция IDCODE, но может и другая, например, SAMPLE. Во избежание этого сброса следует проводить контроллер TAP через безопасное состояние IDLE, в котором все рабочие установки сохраняются.

Схема ВST содержит целый набор сдвиговых регистров. При проходе по правой ветви графа доступен регистр инструкций длиной от 3 бит. Загруженная инструкция определяет один из регистров данных, доступных при проходе по левой ветви и действия с ними в определенных состояниях TAP-контроллера. Из этих регистров, как минимум, в наличии обычно имеются регистр доступа к внешним выводам чипа и однобитный регистр обхода.

Поскольку в цепочке JTAG-устройств все сдвиговые регистры складываются в один длинный, то регистр обхода позволяет уменьшить эту длину, представляя обойденные устройства всего одним битом. Для этого служит инструкция BYPASS. Поскольку ввод инструкции BYPASS отменяет действие ранее загруженной инструкции, к сожалению, невозможно сохранить состояние блоков ввода-вывода, устанавливаемое инструкциями типа EXTEST и INTEST. Исключением является инструкция CLAMP, после которой можно использовать регистр обхода. Но эта инструкция практически не встречается.

В регистре доступа для каждого блока ввода-вывода ПЛИС, как правило, отведены три последовательных бита: вход (I), выход (O) и запрет выхода (T). Порядок вывода бит на TDO различен для ПЛИС разных фирм. Например, для Xilinx - (T,O,I), а для Altera - (I,T,O).

В состоянии CAPTURE в выбранный сдвиговый регистр записывается текущее состояние. Кстати, для регистра инструкций обычно это код инструкции SAMPLE, а для регистра обхода - логическая единица. В состоянии UPDATE данные из сдвигового регистра переписываются в соответствующий регистр хранения.

Таким образом инструкция SAMPLE не только считывает текущее состояние внешних выводов, но и записывает в регистре хранения управляющие данные. Поэтому, чтобы избежать вывода случайной информации, ее используют перед загрузкой инструкций типа EXTEST или INTEST.

При загрузке инструкции EXTEST выходы регистра хранения определяют состояние выходов чипа, т.е. управляют выходом и его третьим состоянием. Таким образом можно протестировать внешние межсоединения. Инструкция INTEST, напротив, подменяет сигнал вводимый внутрь чипа и служит для проверки самого чипа. Часто обходятся одной инструкцией EXTEST, используя бит входа (I) для ввода в чип как в инструкции INTEST.

Инструкция IDCODE подключает встроенный 32-битный регистр с идентификаторами производителя, модели и версии устройства.

Набор инструкций определяется производителем. Как минимум, присутствуют SAMPLE и BYPASS и EXTEST. Остальные инструкции - дополнительные. Как уже упоминалось, для ПЛИС могут быть специальные инструкции конфигурирования, а для процессоров - чтение результата внутреннего теста.

Производители микросхем предоставляют информацию о конкретной реализации BST для каждого типа своей продукции в виде BSDL-файла (Boundary-Scan Description Language). Чуть более подробно об этом формате можно узнать на http://www.asset-intertech.com.

Доступ к JTAG порту можно организовать при помощи кабеля типа ByteBlaster, подключив им тестируемую систему к параллельному порту компьютера. В тестируемой системе рекомендуется установить подтягивающие резисторы (PullUp's) и керамический конденсатор на питании вблизи ответного разъема ( что я успешно применяю в своем интерфейсе JTAG на микросхеме 74НС244, поставив керамический конденсатор на ее питание, если ее учитывать, что питание иногда приходится брать с ресивера……..) . Для устойчивой работы выход TDO желательно буферизовать. Например, через два инвертора типа К561ЛН2.

JTAG Boudaty-Scan Test (BST)

В 1985 сформировалась специальная группа ведущих производителей электроники - JTAG (Joint Test Action Group). Для решения проблем тестирования JTAG выдвинула как промышленный стандарт спецификацию IEEE Std 1149.1-1990 (IEEE Standard Test Access Port and Boundary-Scan Architecture).

Встраивание архитектуры BST в современные чипы обеспечивает доступ к выводам чипа (точнее, к специальным блокам ввода-вывода) с помощью 4-х проводного последовательного интерфейса JTAG. Эта архитектура позволяет не только контролировать их состояние, но и управлять ими. Таким образом можно обойтись без громоздких пробников с физическим контактом.

В дополнении к этому, эта архитектура может быть дополнена возможностью обмениваться и иной информацией с чипом. Например, получать результат внутреннего теста, как это делается в современных процессорах. В ПЛИС (программируемых логических интегральных схемах) эта архитектура обеспечивает альтернативную (или основную) возможность ввода конфигурационных данных.

Необходимо отметить, что для подобных целей используются также и другие последовательные интерфейсы. Например, 2-х проводный I2C требует меньше аппаратных затрат и, что более важно, времени для доступа к устройствам. Однако, преимуществом архитектуры BST является отсутствие необходимости явного задания адресов устройств, поскольку все JTAG-устройства объединяются в последовательную цепочку и неявно адресуются своим положением в ней.

Как видно из графа, TAP-контроллер перейдет в исходное состояние RESET из любого другого не более чем за 5 импульсов TCK при TMS=1. При этом произойдет сброс всей схемы BST, а в регистр инструкций запишется значение по умолчанию (как правило, инструкция IDCODE, но может и другая, например, SAMPLE. Во избежание этого сброса следует проводить контроллер TAP через безопасное состояние IDLE, в котором все рабочие установки сохраняются.

Схема ВST содержит целый набор сдвиговых регистров. При проходе по правой ветви графа доступен регистр инструкций длиной от 3 бит. Загруженная инструкция определяет один из регистров данных, доступных при проходе по левой ветви и действия с ними в определенных состояниях TAP-контроллера. Из этих регистров, как минимум, в наличии обычно имеются регистр доступа к внешним выводам чипа и однобитный регистр обхода.

Поскольку в цепочке JTAG-устройств все сдвиговые регистры складываются в один длинный, то регистр обхода позволяет уменьшить эту длину, представляя обойденные устройства всего одним битом. Для этого служит инструкция BYPASS. Поскольку ввод инструкции BYPASS отменяет действие ранее загруженной инструкции, к сожалению, невозможно сохранить состояние блоков ввода-вывода, устанавливаемое инструкциями типа EXTEST и INTEST. Исключением является инструкция CLAMP, после которой можно использовать регистр обхода. Но эта инструкция практически не встречается.

В регистре доступа для каждого блока ввода-вывода ПЛИС, как правило, отведены три последовательных бита: вход (I), выход (O) и запрет выхода (T). Порядок вывода бит на TDO различен для ПЛИС разных фирм. Например, для Xilinx - (T,O,I), а для Altera - (I,T,O).

В состоянии CAPTURE в выбранный сдвиговый регистр записывается текущее состояние. Кстати, для регистра инструкций обычно это код инструкции SAMPLE, а для регистра обхода - логическая единица. В состоянии UPDATE данные из сдвигового регистра переписываются в соответствующий регистр хранения.

Таким образом инструкция SAMPLE не только считывает текущее состояние внешних выводов, но и записывает в регистре хранения управляющие данные. Поэтому, чтобы избежать вывода случайной информации, ее используют перед загрузкой инструкций типа EXTEST или INTEST.

При загрузке инструкции EXTEST выходы регистра хранения определяют состояние выходов чипа, т.е. управляют выходом и его третьим состоянием. Таким образом можно протестировать внешние межсоединения. Инструкция INTEST, напротив, подменяет сигнал вводимый внутрь чипа и служит для проверки самого чипа. Часто обходятся одной инструкцией EXTEST, используя бит входа (I) для ввода в чип как в инструкции INTEST.

Инструкция IDCODE подключает встроенный 32-битный регистр с идентификаторами производителя, модели и версии устройства.

Набор инструкций определяется производителем. Как минимум, присутствуют SAMPLE и BYPASS и EXTEST. Остальные инструкции - дополнительные. Как уже упоминалось, для ПЛИС могут быть специальные инструкции конфигурирования, а для процессоров - чтение результата внутреннего теста.

Производители микросхем предоставляют информацию о конкретной реализации BST для каждого типа своей продукции в виде BSDL-файла (Boundary-Scan Description Language). Чуть более подробно об этом формате можно узнать на http://www.asset-intertech.com.

Доступ к JTAG порту можно организовать при помощи кабеля типа ByteBlaster, подключив им тестируемую систему к параллельному порту компьютера. В тестируемой системе рекомендуется установить подтягивающие резисторы (PullUp's) и керамический конденсатор на питании вблизи ответного разъема ( что я успешно применяю в своем интерфейсе JTAG на микросхеме 74НС244, поставив керамический конденсатор на ее питание, если ее учитывать, что питание иногда приходится брать с ресивера……..) . Для устойчивой работы выход TDO желательно буферизовать. Например, через два инвертора типа К561ЛН2.